網口在NB、MB、IP-CAM…等產品上屬於相當常見的端口,因網路有可能佈線至戶外,受到EOS突波干擾而造成網路功能異常的機率較高,故有必要在網口設計有效率的ESD/EOS防護對策。

如圖一所示,網口的架構由外部往內可大致切分成3大部分: (1) RJ45 connector, (2) Transformer, (3) LAN PHY。(1)至(2)之間稱之為一次側(Primary side),當Surge測試規格較高時,在一次側transformer中心抽頭處可考慮採用高Surge耐受度的元件保護Bob Smith電路;(2)至(3)之間則為二次側(Secondary side),最新的電路設計趨勢是將保護器件設計在此區域,用以將 transformer隔離過後的突波能量進一步抑制,大幅降低後端LAN PHY受外界異常干擾的威脅。

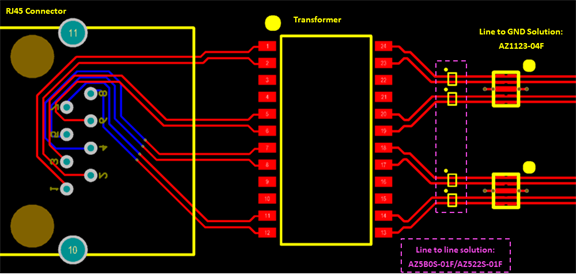

圖一、網口架構示意圖

網口的Surge測試會分為Differential mode跟Common mode兩個測項來進行,故在防護對策上的建議用料亦有所不同。Differential mode主要是針對差動訊號線之間做Surge測試,此時會建議採用雙向保護元件,在differential mode Surge測試時Surge元件導通示意如圖二所示。

圖二、Differential mode Surge test 防護元件導通示意圖

Common mode Surge是將所有網路訊號線同時對地做Surge測試,此時雖然一次側可宣洩大部分能量,但亦會有少部分能量耦合至二次側,此時二次側的ESD/EOS保護元件將啟動把Common mode Surge測試時的能量宣洩至地,示意如圖三所示。

圖三、Common mode Surge test 防護元件導通示意圖

| Interface | Protection | Parts | Package | VRWM (V) | VBR (V) | Vclamp(ESD) | CIn(Typ.) | Ipp(8/20µs) |

|---|---|---|---|---|---|---|---|---|

| 10/100/1000Mbps Ethernet |

Line to GND | AZ1213-04F |

4 I/O Pins DFN2510P10E 2.5x1.0x0.5 mm |

3.3 | 5 | 6.5 | 2.1pF | 20A |

| Line to Line | AZ3125-08F |

4 I/O Pins DFN3020P10E 3x2x0.55 mm |

2.5 | 3 | 8 | 1.7pF | 45A | |

| LED control signal | AZ5883-01F |

1 I/O Pins DFN1006P2E 1.0x0.6x0.5 mm |

3.3 | 4.5 | 5 | 70pF | 52A | |

| 2.5/5/10Gbps Ethernet |

Line to GND | AZ1123-04F |

4 I/O Pins DFN2510P10E 2.5x1.0x0.5 mm |

3.3 | 5 | 10 | 0.2pF | 6.5A |

| Line to Line | AZ5B0S-01F |

1 I/O Pins DFN0603P2Y 0.6x0.3x0.3 mm |

2 | 5.5 | 5.5 | 0.18pF | 7A | |

| Line to Line | AZ522S-01F |

1 I/O Pins DFN1006P2E 1.0x0.6x0.5 mm |

2 | 5.5 | 6.5 | 0.2pF | 6.5A | |

| LED control signal | AZ5883-01F |

1 I/O Pins DFN1006P2E 1.0x0.6x0.5 mm |

3.3 | 4.5 | 5 | 70pF | 42A |

表一、Ethernet ESD/EOS保護方案一覽表

晶焱科技對於網口ESD/EOS完整對策如表一所示,以10Gbps網口為例,Differential mode防護的建議料件有兩種封裝選擇,分別為DFN0603P2Y(0201)封裝的AZ5B0S-01F或DFN1006P2E(0402)封裝的AZ522S-01F,這兩顆元件的寄生電容皆在0.2pF左右,單體皆可承受IEC61000-4-5 Surge (8/20μs) 約6.5A。Common mode 的防護對策則推薦4通道的防護對策AZ1123-04F,寄生電容亦在0.2pF左右,單體亦可承受IEC61000-4-5 Surge (8/20μs)約6.5A。AZ1123-04F的封裝為DFN2510P10E,PCB Layout走線可採順線(feed-through)方式,設計上非常便利,可參考圖四的示意圖。上述10Gbps網口EOS/ESD防護對策中,推薦的防護元件本身寄生電容小,對訊號品質影響較小,且單體耐受佳,非常適合放在網口高速訊號上做使用。

圖四、10Gbps網口ESD/EOS元件PCB Layout示意圖

此外,根據長年來進行網口進行ESD/EOS測試的經驗,較常遇到EOS或ESD (Air Discharge)能量耦合至RJ45 LED控制訊號,導致LAN PHY損壞的問題,如圖五所示。故建議在設計線路時,在LED的控制訊號線亦加上防護對策,以避免此問題的發生。

圖五、網口ESD測試示意圖

網路已成大眾生活中必備的工具,故建議在設計系統的初期就先將相對應的防護對策設計至電路中,以避免未來安規測試無法通過的難題,同時可降低市場上因EOS/ESD而導致網口不良的問題發生。若因成本因素決定不在較低階機種進行防護,亦建議在相關位置設計預留保護元件的封裝位置,避免日後遭遇市場返修問題,甚或品牌客戶要求提高規格時需要再花費時間及物力進行改版的難題。