隨著高清晰影像的需求逐漸提高,沒有高解析度的顯示器是無法滿足使用者的需求。而VESA釋出DP2.0的規格最高可以提供80Gbps 的傳輸速率,憑藉著出色的傳輸效能,可以輸出16K@60Hz及8K@120Hz最佳解析度的影像來滿足使用者需求。為實現如此高速的傳輸速度,DP2.0控制晶片必須使用先進的半導體製程技術,但也造成DP2.0控制晶片對靜電放電(ESD)的耐受能力快速下降。

DP2.0分為三種不同標準,按照頻寬分為UHBR 10、UHBR 13.5、UHBR 20(如圖一所示),UHBR 10每通道頻寬為10Gbps,DisplayPort與USB Type C接口皆可以採用,而UHBR 13.5、UHBR 20就不一樣了,只能建構在USB Type C的接口上,此介面除了可以將傳輸速率提高到80Gbps,而且USB PD供電最高還可以達到100W來實現快速充電。

| Display Port 2.0: UHBR Modes | ||

| Standard | RAW | Interface Port |

| UHBR 10 | 40 Gbps | Display Port / USB Type-C |

| UHBR 13.5 |

54 Gbps | USB Type-C |

| UHBR 20 | 80 Gbps |

USB Type-C |

圖一: DisplayPort 2.0: UHBR Modes

未來USB Type C接口將成為電視、螢幕、個人電腦及筆電…等消費性電子產品的主流接口。與傳統USB相同,USB Type C在系統上是外露給使用者隨時可以插拔的接口,最普遍的應用就是隨插即用、隨拔即關,然而這個熱插拔動作卻也經常是造成電子系統工作異常、甚至造成USB Type C控制元件毀壞的元兇,因為這樣的動作相當容易造成ESD等暫態雜訊問題。在熱插拔中,由於接口端的訊號線已經帶電,這樣的帶電電纜在接觸系統時,將形成放電動作。這種現象等同於靜電放電效應會對系統產生嚴重破壞,一般稱這種現象為直接放電。目前在系統的靜電放電測試上,越來越多的廠商要求以Direct-Pin Injection方式測試產品,以此來模擬系統在用戶端使用時最常遭受到的ESD事件。

在ESD的系統測試要求方面,除了必須通過IEC61000-4-2的規範外,有部份品牌廠商甚至規範其產品USB Type C連接器需以Direct-Pin Injection的測試方式通過±8kV的ESD轟擊。因此使用ESD保護元件於USB Type C介面來防止ESD事件對資料傳輸的干擾是絕對需要的。

對於DP2.0的高速介面而言,在選擇ESD/EOS保護元件時必須考慮到:

1. 為確保DP2.0高速訊號傳輸時的訊號完整性,所以選擇ESD保護元件時,須選擇其寄生電容較低的ESD保護元件,建議寄生電容低於0.2pF。

2. 防護元件對ESD的耐受能力必須要高,最少要能承受IEC 61000-4-2接觸模式8kV ESD的轟擊。

3. ESD Clamping voltage是最重要的參考參數, ESD保護元件若要對系統提供有效保護,最需要考慮箝制電壓是否夠低,使得ESD的能量能被箝制 在更低的電壓以防止系統內部電路受到干擾或損毀,此箝制電壓是判斷ESD保護元件對於系統電路保護效能最重要的參數。

4. USB PD充電技術可以支援四段電壓(5V/9V/15V/20V),頻繁的熱插拔電源線將極易引發ESD/EOS問題,因此需在系統上採用更加完善的外部突波ESD/EOS保護方案設計。

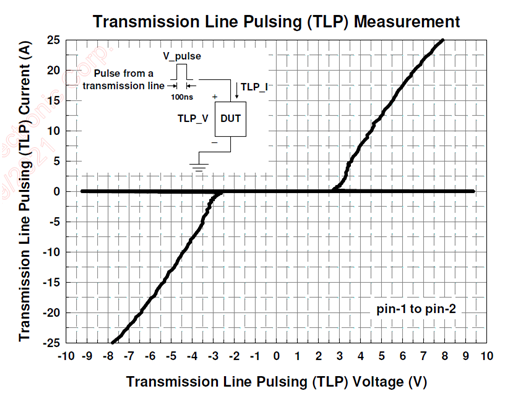

晶焱科技擁有先進的ESD防護設計技術,特別針對DP2.0的需求推出AZ5B0S-01F。為避免防護元件的寄生電容影響DP2.0差動訊號的高速傳輸,AZ5B0S-01F的寄生電容已低於0.2pF,能夠順利的通過Eye Diagram測試。最重要的是AZ5B0S-01F產品擁有極低的ESD箝制電壓,能夠有效地協助DP2.0介面通過Direct-Pin Injection±8kV的靜電放電轟擊。圖二為利用TLP量測AZ5B0S-01F產品的電流對電壓曲線。在IEC 61000-4-2接觸模式8kV的ESD轟擊下(等效TLP電流約為16A),箝制電壓僅有5.5V,能有效避免系統產品於ESD測試時發生資料錯誤、當機甚至損壞的情況。

圖二、AZ5B0S-01F的ESD箝制電壓特性曲線

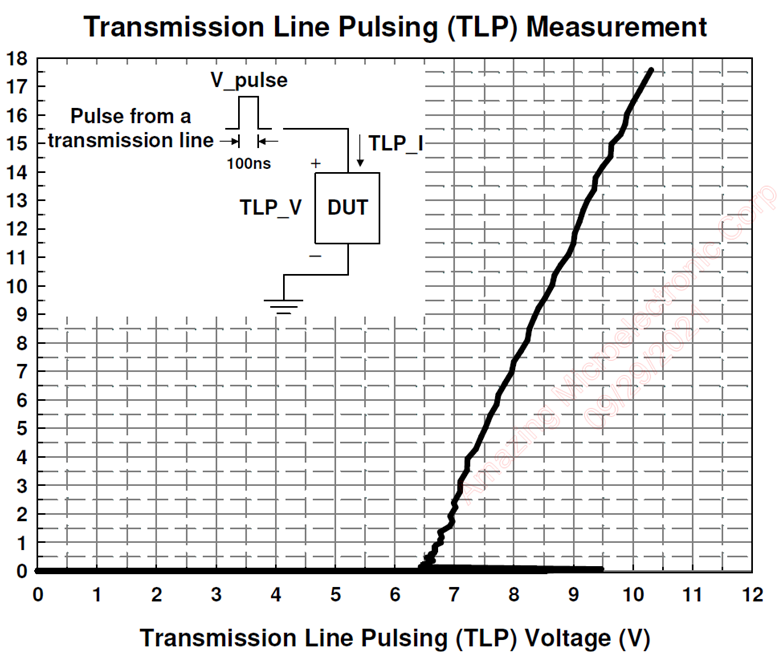

其餘的訊號線(AUX/D+/D-/CC/HPD)建議採用DFN1006P3X封裝的AZ5515-02F,其單體可耐受IEC61000-4-5 (8/20µS)的能量約11A,ESD箝制電壓僅10V@16A(如圖三所示)。

圖三、AZ5515-02F的ESD箝制電壓特性曲線

此接口還可提供快速充電,在電源端需依設計的電壓選用一顆合適的EOS防護元件(如圖 AZ3105-01F/AZ4510-01F/AZ4516-01F/AZ4520-01F)來保護,此時就可以完整地保護此接口不受ESD/EOS的威脅,圖四即為完整的DP2.0介面的ESD/EOS解決方案保護線路。

圖四、DP2.0介面的ESD/EOS解決方案保護線路