画像処理技術が絶えず向上するにつれ、携帯電話とカメラの画素数が更に多くなっていき、ハードディスクの容量も更に多くなっています。ユーザーのデータ伝送に対して絶えず要求を増して、より速い伝送速度も求めています。しかし、USB-IFによるUSB4規格は伝送速度を40Gbit/sまで向上し、更に高まっているユーザーの速度への要求に対応することができますが、この高速の伝送速度を実現するために、USB4制御チップのESD(静電気放電)耐久力がみるみるうちに落ちています。

USB4はUSB Type Cのフィジカルインターフェース上に構築します。このインターフェースは伝送速度を40Gbit/sまで向上するだけではなく、USB PDの充電規格で最高100Wの快速充電を実現できます。今後、USB Type Cインターフェースは個人用のデスクトップPC、ノートPC、タブレット、スマートフォンなど消費性電子製品の主流となるインターフェースになる見通しです。

従来のUSBと同様、USB4はシステム上、ユーザーが随時抜き差しするインターフェースがむき出しになります。差し込んでからすぐ使用、抜いたらすぐ終了が最も一般的な利用スタイルですが、この抜き差しの動作も常に電子系統の動作異常を引き起こし、USB Type C制御コンポーネント破損の元凶にさえなります。なぜなら、このような動作はESDなど一時的なノイズの問題が発生しやすくなるからです。ホットスワップ中は、インターフェース側の信号ケーブルがすでに帯電しているため、このような帯電しているケーブルがシステムに接触する際、放電が発生します。

この現象は、システムに静電気放電効果に匹敵する重大な損傷を与え、一般的にこの現象は直接放電と呼ばれています。現在、システムの静電気放電試験を行う際、ますます多くのメーカーがピン端子のダイレクト印加方式による製品テスト(図1参照)を要求するようになり、こうして、ユーザー側がシステムを使用する際に最も頻繁に受けるESDインシデントをシミュレートします。

図1: ダイレクトピン挿入テスト用装置

ESDのシステムのテスト要件について、IEC61000-4-2の規定を必ず合格することに加え、一部のメーカーは、自社製品のUSB TypeCコネクタがダイレクトピン印加法による±8kV ESD衝撃に合格する必要があることを規制しています。そのため、ESD防護ダイオードでUSB Type CインターフェースがESDインシデントでデータ伝送の妨害防止は絶対必要です。

また、電子製品が世界各地に急速に浸透してきましたが、整備不十分なインフラや異常気象の多発により、多くの地域で電子製品が電気的オーバーストレス(EOS)を受ける可能性が大幅に上昇し、返品修理の割合が明らかに増加しています。

現在の試験基準では主にIEC61000-4-5の国際規格を採用して電気的干渉や一時的なノイズ、ホットスワップなどのシミュレーションでEOSインシデントを発生させます。測定する波形は電圧が1.2/50μs、電流が8/20μsです。一部のメーカーはESDダイレクトピン印加テストを社内で規定するだけではなく、EOS ダイレクトピン印加テスト(図2参照)も追加しています。

図2.EOS ダイレクトピン印加テスト用装置

USB4の高速インターフェースについて、ESD/EOS防護コンポーネントを選択する際、以下の事項を考慮する必要があります。

1. USB4高速信号伝送時の信号の完全性を確保するため、ESD防護コンポーネントを選択する際、寄生容量が低いESD防護コンポーネントを選択する必要があります(0.2pF未満推奨)。

2. 防護コンポーネントはESDに対して高い耐久力が必要です。少なくともIEC 61000-4-2接触モードの8kV ESDの衝撃に耐えられる必要があります。

3. ESDクランプ電圧は最も重要なパラメータです。ESD防護コンポーネントでシステムに対して効果的な防護を行う場合、最も考慮すべきはクランプ電圧の大きさであり、ESDエネルギーをより低い電圧でクランプすることで、システムの内部回路への干渉や損傷を防ぐことができます。クランプ電圧は、システム回路のESD防護コンポーネントの防護性能を判断する最も重要なパラメータです。

4. USB PD充電技術は4段階の電圧(5V/9V/15V/20V)に対応可能であり、頻繁に抜き差しするホットスワップ電源ケーブルはESD/EOSの問題を極めて発生しやすくなるため、システムに外部からのESD/EOSに完全対処可能な防護対策設計を講じる必要があります。

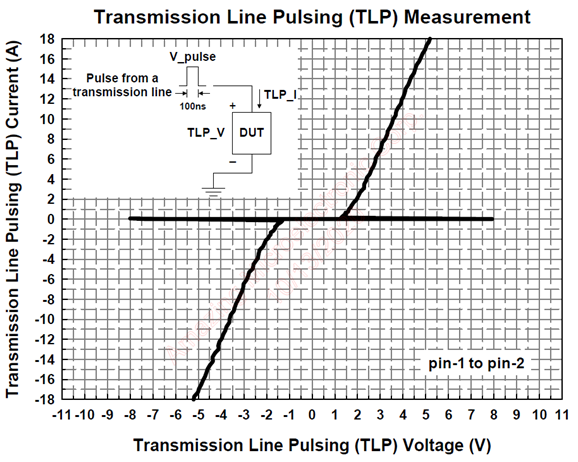

先進的なESD防護設計技術を擁する晶焱科技は、USB4.0に対応したAZ5B9S-01Fを独自に設計しました。 防護コンポーネントの寄生容量がUSB4の平衡接続 による高速伝送へ影響を及ぼさないように、AZ5B9S-01Fの寄生容量は0.2pFを下回っていますので、40Gbit/sのアイパターン測定に合格できます。最も重要なことは、AZ5B9S-01F製品のESDクランプ電圧が非常に低く、USB4インターフェースがダイレクトピン印加テストの8kVの静電気放電の衝撃に耐えられることです。図3はTLP測定を利用したAZ5B9S-01F製品の電流対電圧の曲線です。IEC 61000-4-2接触モード8kVのESD衝擊(TLP電流約16Aに相当)において、クランプ電圧はわずか4.6Vであり、システム製品のESDテスト時のデータエラー、故障、損壊などを防止します。

図3. AZ5B9S-01FのESDクランプ電圧の特性曲線

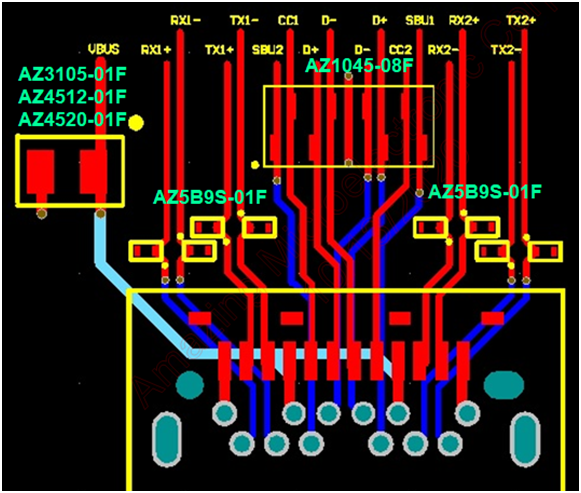

電子製品の小型化、スリム化が進むにつれ、プリント基板(PCB)もますます小さくなっていますが、強力な製品機能が求められている中、ネットワークも更に複雑になっているため、PCBの面積あたりのコストが増えて、製品設計時に相当な困難に遭遇してしまいます。AZ5B9S-01F製品は超小型DFN0603P2Yパッケージを採用していますので、寸法はわずか0.6mm × 0.3mm、高さはわずか0.3mmです。USB4の4組の差動[ペア](TX、RX)を主に防護するほか、AZ1045-08Fを別途使用すればその他信号ライン(D+/D-/CC/SBU)も防護が可能です。特にAZ1045-08Fでは、インターレース方式のリード線を採用しているため、PCBレイアウトにフィードスルー設計が可能になりますので、面倒な配線作業が不要となり、製品設計段階でのPCBレイアウト作業の短縮化だけでなく、PCB面積の削減によるシステムコストの削減を実現できます。このインターフェースは急速充電も可能です。電源側では、設計された電圧に従って適切なEOSコンポーネント(AZ3105-01F / AZ4512-01F / AZ4520-01Fなど)を選択して防護する必要があります。このとき、インターフェースをESD / EOSの脅威から完全に防護することができます。図4は、USB4インターフェースのESD / EOS対策の完全な防護回路です。