摘要:USBインターフェースプロトコルが進化、完全化するにつれ、スマート製品の多くがUSB Type-Cインターフェースを採用しています。対応するAVデータの伝送コンテンツが多彩になって、伝送速度もより速くなっていますが、当然信号伝送はより外部サージによる妨害を受けやすくなります。そのため、TVSを利用したサージ防護対策もさらに厳しくなりますが、対策方法を選択する際TVSの使用電圧などのパラメータを考慮しない場合、クランプ電圧の低いTVS製品の選択をひたすら追求してしまうと、TVSにラッチアップの危険性が生じてType-Cインターフェースの正常な通信に影響を及ぼし、酷い場合はEOS(電気的オーバーストレス) で電気回路を損壊します。

電子製品の接続インターフェース内の信号ケーブルと電源ケーブルの配線複雑化に対して、正確かつ効果的な過度サージ防護を行う場合、接続インターフェースにTVSを追加することが恐らく最も効果的な防護対策です。

1. Type-C概要 USB(Universal Serial BUS)は汎用シリアルインターフェースであり、伝達速度が速い、フレキシブルな接続、使いやすい、ホットスワップ対応、独立給電などの利点があり、様々な電子製品で幅広く利用されています。USBインターフェースの定義は最初期はUSB1.0でしたが、最新のUSB 4へ更新されています。そのうち、現在最も普及している接続インターフェースプロトコルはUSB 3.1です。

USB 3.1プロトコルはUSB 2.0のようにただインターフェースの種類をType AとType Bと定義するだけではなく、3種類の接続インターフェース基準(Type-A(Standard-A)、Type-B(Micro-B)、Type-C)と2種類の技術基準(USB 3.1 Gen1、USB 3.1 Gen2)に分かれます。

そのうち、Type-C接続インターフェースは携帯電話、タブレット、ノートパソコンなどの電子製品で幅広く利用されています。

| USB 公式規格名 | 旧規格名 | 理論上最大伝送速度 | 公式市場コード | 仕様発行日 | |

| USB 2.0 | USB1.0 | 1.5Mbps | Low-Speed | 1996年1月 | |

| USB 2.0 | USB1.1 | 12Mbps | Full-Speed | 1998年9月 | |

| USB 2.0 | USB2.0 | 480Mbps | High-Speed | 2000年4月 | |

| USB 3.2 | USB3.1 Gen 1 | 5Gbps |

Super-Speed USB | 2008年11月 | |

| USB 3.2 | USB3.1 Gen 2 | 10Gbps | Super-Speed USB 10Gbps | 2013年6月 | |

| USB 3.2 |

USB3.2 Gen 2x2 |

20Gbps | Super-Speed USB 20Gbps | 2017年9月 | |

| USB 4 |

USB4 Gen 3x2 |

40Gbps | USB4 40Gbps | 2019年9月 | |

表1. USB 各バージョン情報

USB 3.2 Gen2×2プロトコルType-Cインターフェースは、信号伝送速度が最高20Gbpsに達し、PD(Power Delivery)プロトコル対応、最高電圧20V・最高電流5Aにより100Wの伝送電力を実現します。Type-Cはデータの伝送速度を高めるだけではなく、電源の伝送電力が増大するため、実際の用途において、データ伝送がサージによる妨害を防止して、電力伝送が安定化するよう、接続インターフェースをTVSで防護することは特に重要になってきています。

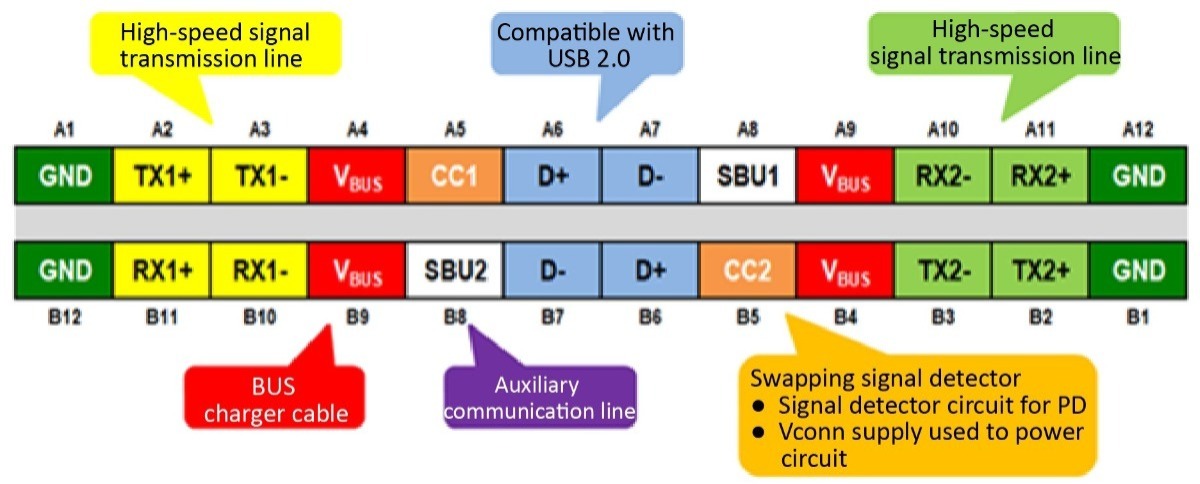

図1. USB Type-C レセプタクルピン

2. ラッチアップとは何か?

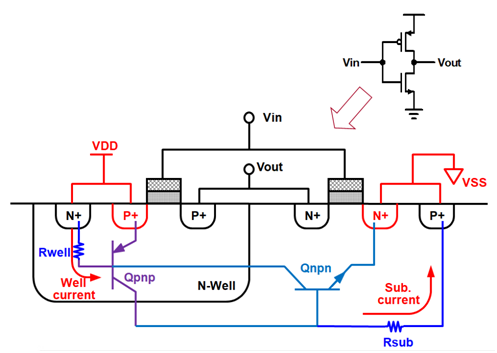

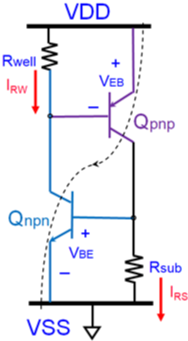

ラッチアップ(Latch-up)はCMOS製造工程中に発生する寄生効果であり、NMOSソース、またはサブストレート、n-ウェル 、PMOSのソース構成のPNPN接合から発生します。一部のBJTが順方向にバイアスされている場合、ポジティブフィードバックを構成してラッチアップが発生する可能性があります。

図2. CMOS内部のPNPN接合

図3. ラッチアップの等価回路

サイリスタ回路のPNPN接合が誘発されていない場合、2個のBJTが中断状態になり、コレクタ電流はコレクタからベースへ逆電流を構成するため、電流の増大は非常に小さく、この時ラッチアップは発生しません。外部からの妨害によって1個のBJTのコレクタ電流が突如一定値になった場合、他のBJTへフィードバックします。2個のBJTが誤誘発によって導通し、VDD-GND(VSS)間低インピーダンス通路を形成します。その後、外部からの妨害が消失して2個の三極管の間に正のフィードバックを形成し、VDD-GND(VSS)間に大きな電流が止まらずここでラッチアップが発生します。

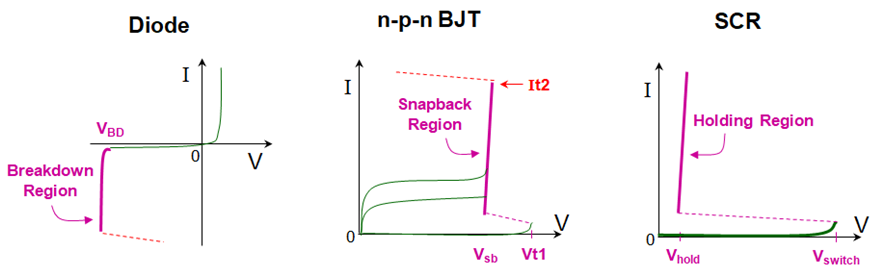

半導体用ウエハーで実際に利用するにあたってラッチアップが発生しやすい原因は主に以下の原因があります。 1. ウエハーで電気工事を行う際、VDD電圧の変化が大きすぎるため、ラッチアップが発生する可能性があります。 2. ESD、サージなどが発生する際、電気回路中に大きな電流が生じてラッチアップを引き起こす可能性があります。 3. 電気回路の負荷が過剰な場合、電源とGNDの電圧に変化が生じ、SCRのうちの1個のBJTがオンになって、ラッチアップが発生する可能性があります。 4. 使用電圧が3.3V以上の信号ケーブルまたは電源でスナップバック (snap-back) 電圧が3.3V未満の保護部品を使用している場合、上記の過度サージが発生する際、ラッチアップを引き起こし深刻なシステム焼損の原因になります。 市販のTVS製品の設計は多種多様ですがですが、晶焱科技のTVS製品は従来のダイオード設計、NPN接合のBJT設計、サイリスタ設計の3種類があります。3種の特性曲線は以下の通りです。

図4. TVS の特性曲線

Type-Cインターフェースの電気回路の防護において、TVSの選択が正しくなく、サイリスタ設計のTVSがVBUS端子 またはCCピン回路で利用される場合、 ラッチアップのリスクがさらに増し、当然信号ケーブルも同様にこのリスクが発生します。主な原因はESD、サージなど 接続インターフェース回路と結合する際、外部の過剰サージがTVSの絶縁破壊電圧より高い場合、TVSが導通されます。選択が正しくない場合、TVSをオンにした後のスナップバック電圧(Vsb または Vhold)が正常な使用電圧Vbusまたはデータ信号電圧の最大値VMAXよりも低い場合、外部の過剰サージによる妨害が消えても、TVSも導通状態のままであり、このとき電流が大量に増加して、電源の電圧も低くなるか、正常な信号伝送が妨害され、深刻な場合、TVSがショートして、部品または回路全体がEOSで損壊します。

Type-Cインターフェースが使用時常にホットスワップの場合、抜き差し時のサージやESD対策ケーブルの放電時の過度サージよる妨害が極めて発生しやすいです。TVSをType-Cインターフェースで利用中にラッチアップ発生のリスク回避のため、当社はTVS選択時、TVSの使用電圧VRWMが電気回路の正常な使用電圧または信号電圧の最大値を確実に上回るだけではなく、TVSの導通後、スナップバック特性のTVS製品に発生するスナップバック後の最低電圧Vsb またはVholdが必ず電気回路の正常な使用電圧の最大値を上回るよう配慮しています。

3. Type-Cインターフェースの推奨TVSソリューション

完全なType-Cインターフェースは送電線とデータ線の数が比較的多いため、晶焱科技は信号別にVBUS送電線保護、TX、RXデータ線保護、D+、D-、CC、SBUデータ線保護の3つの箇所でTVS保護ソリューションを推奨しています。

(1) Type-CはPDプロトコルに対応し、一般的に使用されるVBUS伝送電圧は5Vと12V、最大電圧で20Vであるため、当社はVBUS保護のために適切な使用電圧のTVS保護ソリューションを選択する必要があります。クランプ電圧が低いTVSを選択しながら、ラッチアップ発生を防止する必要もあります。次の表は、当社がType-CVBUS送電線に対して推奨するESDおよびEOS保護ソリューションです。

| 部品番号 |

用途 |

VRWM (V) | VCL-ESD(V) @ 8kV | VCL-Surge (V) @ 5A | IPP(A) | パッケージ |

| AZ3105-01F | Only for 5V VBUS | 5 | 6 | 6.4 | 80 | DFN1610P2E |

| AZ4507-01F | Only for 5V VBUS | 7 | 10 | 8.5 | 100 | DFN1610P2E |

| AZ4510-01F

| For VBUS ≤ 10V | 10 | 13 | 21 | 80 | DFN1610P2E |

| AZ4512-01F | For VBUS ≤ 12V | 12 | 15 | 14.5 | 38 | DFN1610P2E |

| AZ4520-01F | For VBUS ≤ 20V | 20 | 25.5 | 25.5 | 24 | DFN1610P2E |

| AZ4307-01F | For VBUS ≤ 7V | 7 | 9.5 | 8.3 | 180 | DFN2020P2E |

| AZ4310-01F | For VBUS ≤ 10V | 10 | 13 | 11.7 | 150 | DFN2020P2E |

| AZ4712-01F | For VBUS ≤ 12V | 12 | 15 | 14.8 | 225 |

DFN2020P2E |

| AZ4715-01F | For VBUS ≤ 15V | 15 | 18 | 17 | 170 | DFN2020P3E |

| AZ4718-01F | For VBUS ≤ 18V | 18 | 22 | 22 | 138 | DFN2020P3E |

| AZ4724-01F |

For VBUS ≤ 20V |

24 | 28 | 28 | 125 | DFN2020P3E |

表2. Type-C VBUS 用TVSソリューション

(2) TX / RXは高速データ伝送線路です。当社はTVS保護ソリューションを選択する場合、Type-Cインターフェ-スの信号品質に影響を与える過剰な電容量を回避するために、低電容量の製品を選択する必要があります。下表は、高速信号TX / RXライン保護方式の場合の当社の推奨ソリューションです。

| 部品番号 |

ライン数 # |

VRWM (V) | VCL-ESD(V) @ 8kV | 電容量 (pf) | パッケージ |

| AZ1043-04F | 4 ライン | 3.3 | 10.5 | 0.45 | DFN2510P10E |

| AZ1043-08F | 8 ライン | 3.3 | 9 | 0.5 | DFN3810P9E |

| AZ1743-04F | 4 ライン | 3.3 | 9.5 | 0.4 | DFN1308P5Z |

| AZ176S-04F | 4 ライン | 1.5 | 4.3 | 0.29 | DFN2510P10E |

| AZ5B8S-01F |

1 ライン |

1.5 | 5.5 | 0.18 | DFN0603P2Y |

表3. Type-C TX/RX用TVSソリューション

(3) USB D+/D-データ線、および補助通信CC、SBU信号線の推奨TVS保護ソリューション

| Part No | ライン数 # | VRWM (V) | VCL-ESD(V) @ 8kV | 電容量 (pf) | パッケージ |

| AZ1045-04F | 4 ライン | 5 | 12 | 0.5 | DFN2510P10E |

| AZ1045-08F | 8 ライン | 5 | 10.5 | 0.5 | DFN3810P9E |

| AZ5425-01F | 1 ライン | 5 | 24 | 0.8 | DFN1006P2E |

| AZ5515-02F | 2 ライン | 5 | 10 | 0.8 | DFN1006P3X |

| AZ5B85-01B | 1 ライン | 5 | 11 | 0.5 | CSP0603P2Y |

| AZC099-04S |

4 ライン |

5 | 11.5 | 1.0 | SOT23-6L |

| AZC199-04S |

4 ライン |

5 | 11 | 1 | SOT23-6L |

表4. Type-C D+/D-/CC/SBU用TVSソリューション

参考文献: [1]. USB 公式ウェブサイトe: https://www.usb.org/