高解像度画像の需要が徐々に高まるにつれ、高解像度ディスプレイはユーザーのニーズを満たすためには欠かせなくなっています。 VESAは、最大80Gbpsの伝送速度を提供できるDP2.0仕様をリリースしました。その優れた伝送性能により、16K@60Hzおよび8K@120Hzの最高の解像度で画像を出力してユーザーのニーズに対応しています。 このような高速伝送速度の実現のためには、DP2.0制御チップは高度な半導体製造技術を導入する必要がありますが、それゆえにDP2.0制御チップの静電放電(ESD)に耐える能力が急速に低下してしまいます。

DP2.0は、帯域幅に応じてUHBR 10、UHBR 13.5、UHBR 20(図1参照)の3つの異なる規格に分けられます。UHBR10の帯域幅はチャネルあたり10Gbpsであり、DisplayPortとUSB Type Cのどちらのインターフェースでも使用できますが、UHBR13.5とUHBR20は異なり、これらはUSB Type Cにのみで使用できます。このインターフェースでは伝送速度を80Gbpsに上げることができ、USB PD電源は最大100Wに高速充電を実現することができます。

| Display Port 2.0: UHBR Modes | ||

| Standard | RAW | Interface Port |

| UHBR 10 | 40 Gbps | Display Port / USB Type-C |

| UHBR 13.5 |

54 Gbps | USB Type-C |

| UHBR 20 | 80 Gbps |

USB Type-C |

図1: DisplayPort 2.0: UHBR モード

将来的にUSB Type Cインターフェースは、テレビ、モニター、デスクトップパソコン、ノートパソコンなど家電製品の主流のインターフェースになります。 従来のUSBと同様に、USB Type Cは、USB Type Cは、システム内でユーザーがいつでも抜き差しできる露出型インターフェースです。最も一般的な利用法は、プラグアンドプレイ、ホットプラグですが、ただし、このホットプラグ操作により、ESDなどの一時的なノイズの問題を引き起こしやすくなるため、電子システムの異常な動作や、 USB Type C制御コンポーネントの破壊の元凶となります。ホットプラグでは、インターフェースの信号ケーブルがすでに帯電されているため、帯電されたケーブルは、システムに接触すると放電を起こします。 この現象は、システムに重大な損傷を与える静電放電効果と同等であり、一般的に直接放電と呼ばれます。 現在、システムの静電放電テストでは、システムをユーザー側で使用したときにシステムが最も頻繁に発生するESDイベントをシミュレートするために、ダイレクトピンインジェクション方式の製品テストを必要とするメーカーが増えています。

ESDシステムのテスト要件に関しては、IEC61000-4-2規範を合格することに加え、一部のメーカーでは、自社製品のUSB TypeCコネクタがダイレクトピンインジェクションテスト方法による衝撃基準の±8kVESDに合格することを必要条件としてます。 したがって、ESDイベントがデータ伝送への干渉防止のため、USB TypeCインターフェースでESD保護コンポーネントを使用することが絶対に必要です。

DP2.0の高速インターフェースの場合、ESD / EOS保護コンポーネントを選択する際に以下の点を考慮する必要があります。

1. DP2.0高速信号伝送中の信号品質を確保するため、ESD保護コンポーネントを選択するときは、寄生容量の小さいESD保護コンポーネントを選択する必要があります。寄生容量は0.2pF未満をお勧めします。

2.保護コンポーネントは、少なくともIEC61000-4-2接触モードの8kVESD衝撃に耐えられるように、ESDに対して高い耐久力を備えている必要があります。

3.ESDクランプ電圧は最も重要な参照パラメータです。システムを効果的に保護するESD保護コンポーネントの場合、最も重要な考慮事項は、クランプ電圧が十分に低いかということです。クランプ電圧が低いと、システムの内部回路が干渉したり損傷したりするのを防ぐために、ESDエネルギーをより低い電圧でクランプすることができます。クランプ電圧は、システム回路のESD保護コンポーネントの保護性能を判断する最も重要なパラメータです。

4.USB PD充電技術は、4つの電圧(5V、9V、15V、20V)に対応できます。電源コードが頻繁にホットプラグすると、ESD / EOSの問題が非常に発生しやすくなるため、システムではより完全な外部サージESD / EOS保護スキームが必要となります。

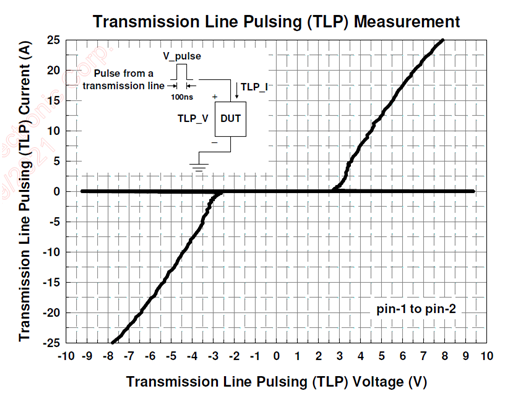

晶焱科技は、特にDP2.0でリリースされたAZ5B0S-01Fのニーズに対応するために、高度なESD保護設計技術を採用しています。 保護コンポーネントの寄生容量がDP2.0差動信号の高速伝送に影響を与えないようにするため、AZ5B0S-01Fの寄生容量は0.2pF未満であり、アイダパターンテストをスムーズにクリアすることができます。最も重要なことは、AZ5B0S-01F製品のESDクランプ電圧が非常に低く、DP2.0インターフェースがダイレクトピンインジェクション法の±8kV静電放電衝撃テストを合格できることです。 図2は、TLPによって測定されたAZ5B0S-01F製品の電流対電圧曲線です。 IEC61000-4-2接触モードでESD衝撃(等価TLP電流は約16A)が8kVの場合、クランプ電圧はわずか5.5Vであり、ESDテスト中のデータエラー、クラッシュ、損傷からシステム製品を効果的に保護します。

図2 AZ5B0S-01FのESDクランプ電圧の特性曲線

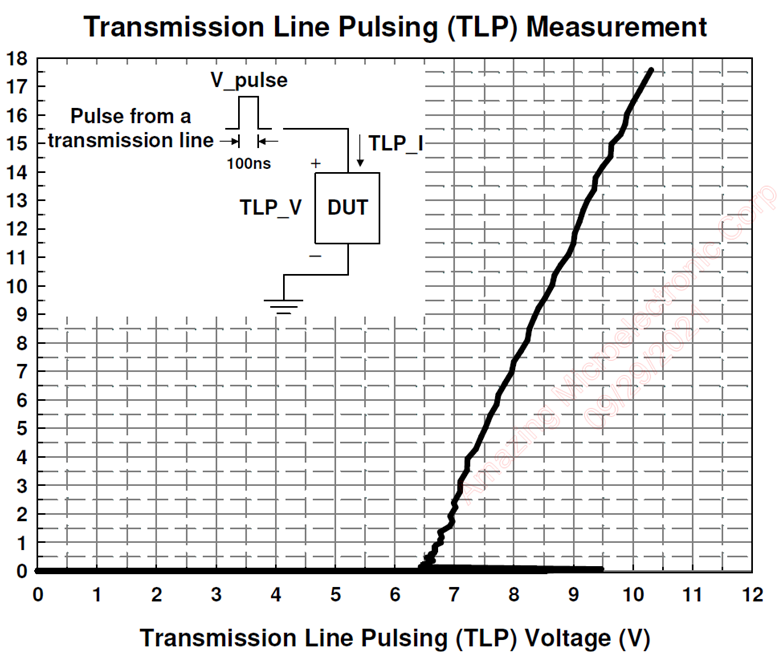

残りの信号ケーブル(AUX / D + / D- / CC / HPD)は、DFN1006P3XパッケージのAZ5515-02Fを使用することをお勧めします。単体で約11AのIEC61000-4-5(8 / 20µS)のエネルギーに耐えることができ、ESDクランプ電圧はわずか10V @ 16Aです(図3参照)。

図3:AZ5515-02FのESDクランプ電圧の特性曲線

このインターフェースは急速充電も可能です。電源側では、保護用に設計された電圧に応じて、適切なEOS保護コンポーネント(図AZ3105-01F、AZ4510-01F、AZ4516-01F、AZ4520-01Fを参照)を選択する必要があります。 この時、インターフェースをESD/EOSの脅威から完全に保護することができます。図4は、完全なDP2.0インターフェースのESD/EOSソリューション保護回路を示しています。

図4:DP2.0インターフェースのESD/EOSソリューションの保護回路